## EE 435

Lecture 40

Switched-Capacitor Amplifiers and Switched-Capacitor Filters

## How important is statistical analysis?

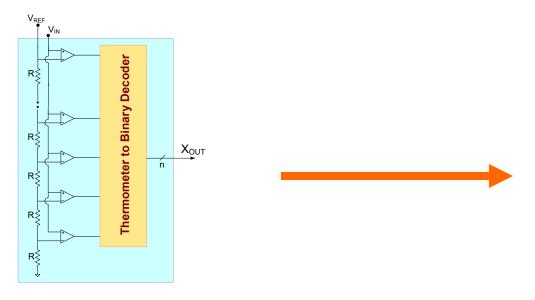

Example: What will be the yield if two of the 7-bit FLASH ADCs with yields of 98.8% are combined to obtain an 8-bit ADC?

$$Y_{ADC} = 1.52 \cdot 10^{-6}$$

- The onset of statistically-induced yield loss can be abrupt

- Intuition is not an acceptable substitute to statistical analysis

- Without statistical analysis/simulation there is a high probability that a data converter will be substantially over designed or under designed and neither is acceptable

#### Review from Last Lecture

#### String DAC Statistical Performance

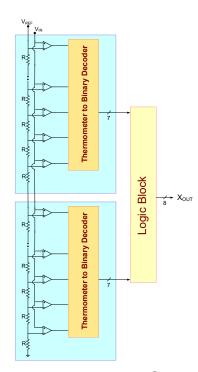

standard deviation of INL<sub>k</sub> assumes a maximum variance at mid-code

It can be shown that INL<sub>k</sub> is Gaussian and

$$\sigma_{INLk \max} = \sigma_{\frac{R_R}{R_{NOM}}} \frac{\sqrt{N}}{2}$$

#### Review from Last Lecture

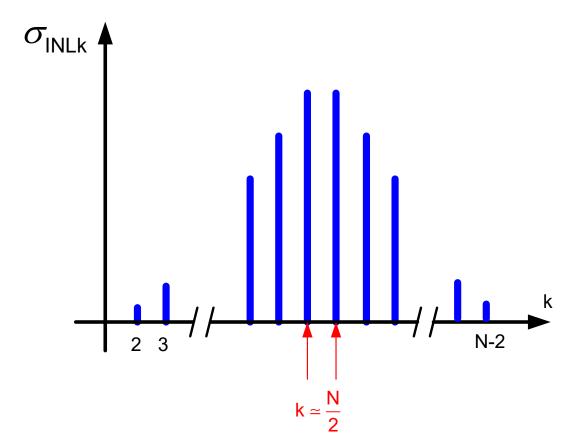

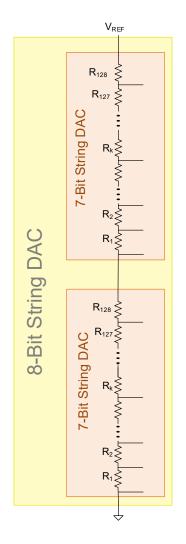

Example 3: What area is needed for obtaining a 99% yield for an 8-bit string DAC and how does that compare to the area required for a 7-bit DAC with the same yield?

$$\sigma_{z} = \sigma_{\frac{R}{R_{N}}} \bullet \frac{\sqrt{N}}{2} = \frac{A_{\rho}}{\sqrt{A}} \bullet \frac{\sqrt{N}}{2} = 0.388$$

$$\frac{\mathsf{A}_{\rho}}{\sqrt{\mathsf{A}}} \bullet \frac{\sqrt{\mathsf{N}}}{2} = 0.388$$

$$\begin{aligned} &A_{\rho}=0.1\mu m & N=256 \\ &A=4.25\,\mu m^2 \end{aligned}$$

$$A = 4.25 \, \mu m^2$$

Area doubled because there are twice as many resistors and each is approximately twice as big so by adding 1-bit of resolution, the area went up by approximately a factor of 4

#### Review from Last Lecture

## How important is statistical analysis?

- Statistical analysis of data converters is critical

- Some architectures are more sensitive than others to statistical variations in components

- The onset of yield loss due to statistical limitations is generally quite abrupt and can have disastrous effects if not considered as part of the design process

Recall examples where  $\sigma_{VOS}$ =5mV compared with  $\sigma_{VOS}$ =1mV

Substantially over-designing to avoid concerns about statistical yield loss is not a practical solution since the area penalty, the speed penalty, and the power penalty are generally quite severe

For the effects of local random variations of a parameter X, generally

$$\sigma_X \propto \frac{A_0}{\sqrt{A_C}}$$

where A<sub>C</sub> is the area of the matching critical components and A<sub>0</sub> is a process parameter

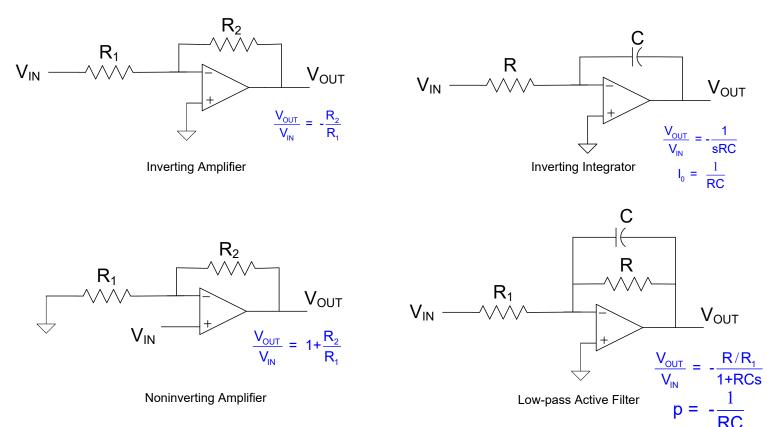

#### Some of the most basic and widely used analog circuits

Not practical to implement on silicon

- Area for R too big

- Area for C too big

- Accuracy of I<sub>0</sub> and p too poor

But ratio accuracy can be very good (0.1% or better with good layout and appropriate area)

#### How bad is the problem?

```

N+ACTV P+ACTV POLY

POLY2

MTL1

MTL2

UNITS

PROCESS PARAMETERS

PLY2 HR

103.2

984

39.7

0.09

0.09

ohms/sq

Sheet Resistance

56.2

118.4

Contact Resistance

0.78

24.0

ohms

Gate Oxide Thickness 144

angstrom

MTL3

N/PLY

N WELL

PROCESS PARAMETERS

UNITS

815

0.05

824

ohms/sq

Sheet Resistance

Contact Resistance

0.78

ohms

```

COMMENTS: N\POLY is N-well under polysilicon.

| CAPACITANCE PARAMETERS Area (substrate) | N+ACTV<br>429 | P+ACTV<br>721 | POLY POLY2 | M1<br>32   | M2<br>17 | M3<br>10 | N_WELL<br>40 | UNITS<br>aF/um^2 |

|-----------------------------------------|---------------|---------------|------------|------------|----------|----------|--------------|------------------|

| Area (N+active)                         |               |               | 2401       | 36         | 16       | 12       |              | aF/um^2          |

| Area (P+active)                         |               |               | 2308       | <i>-</i> 1 | 4.7      |          |              | aF/um^2          |

| Area (poly)                             |               |               | 864        | 61         | /        | 9        |              | aF/um^2          |

| Area (poly2)                            |               |               |            | 53         |          |          |              | aF/um^2          |

| Area (metal1)                           |               |               |            |            | 34       | 13       |              | aF/um^2          |

| Area (metal2)                           |               |               |            |            |          | 32       |              | aF/um^2          |

| Fringe (substrate)                      | 311           | 256           |            | 74         | 58       | 39       |              | aF/um            |

| Fringe (poly)                           |               |               |            | 53         | 40       | 28       |              | aF/um            |

| Fringe (metal1)                         |               |               |            |            | 55       | 32       |              | aF/um            |

| Fringe (metal2)                         |               |               |            |            |          | 48       |              | aF/um            |

| Overlap (N+active)                      |               |               | 206        |            |          |          |              | aF/um            |

| Overlap (P+active)                      |               |               | 278        |            |          |          |              | aF/um            |

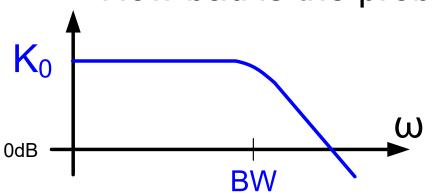

### How bad is the problem?

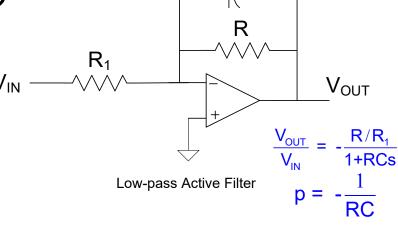

Assume  $|p|=2\pi \cdot 1000$  and pole accuracy needed is 0.1%

$$K_0 = 1 + \frac{R_2}{R_1}$$

Process tolerance on R and C is about ±20%

$$BW_{rad/sec} = -p = \frac{1}{RC}$$

$$R = 20\Omega/\Box$$

and  $Cd = 1pF/\mu^2$  (approximately)

If R=1K $\Omega$ , require 1000/20=50 squares

$$\frac{1}{RC} = 2000\pi \qquad C = \frac{1}{R \cdot 2000\pi} \qquad C = \frac{1}{1000 \cdot 2000\pi} = 0.159 \mu F$$

$$A_{C} = \frac{C}{C_{D}} = \frac{0.159 \mu F}{1 f F / \mu^{2}} = 1.59 \times 10^{8} \mu^{2}$$

Pole tolerance ±40%

#### Both are orders of magnitude unacceptable!

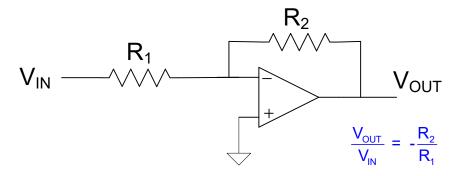

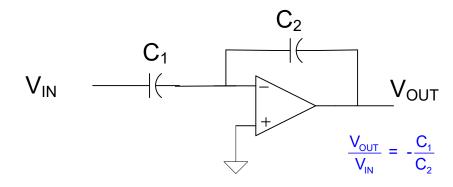

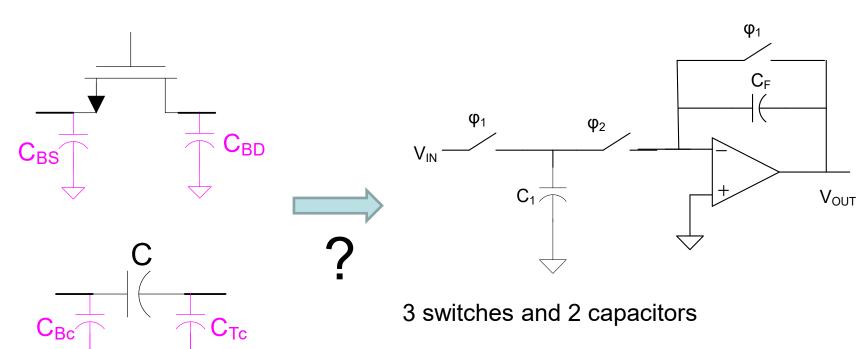

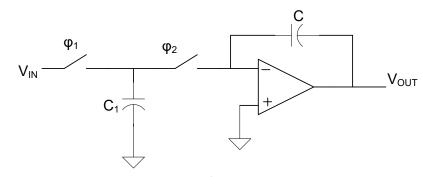

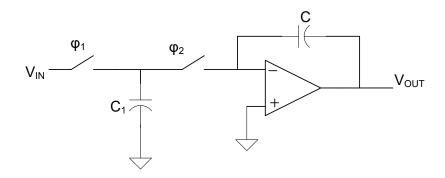

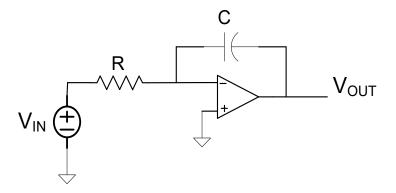

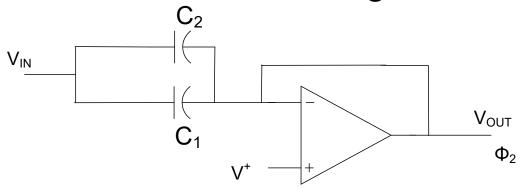

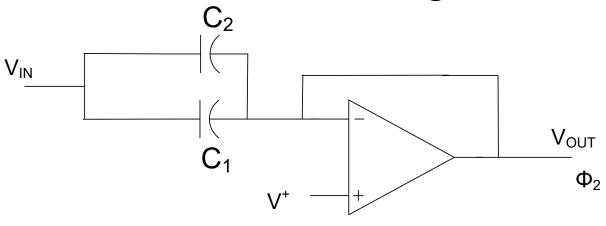

#### An amplifier alternative ?

**Inverting Amplifier**

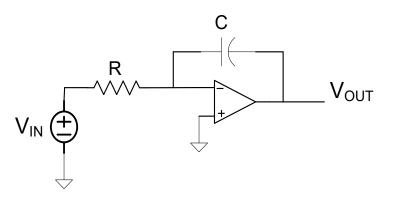

**Inverting Amplifier**

- Capacitor version is area effective and can have very good accuracy

- The node between C<sub>1</sub> and C<sub>2</sub> is a floating node if the Op Amp has a MOS differential pair at the input

- But if we get any charge on the intermediate node there is no way to get it off

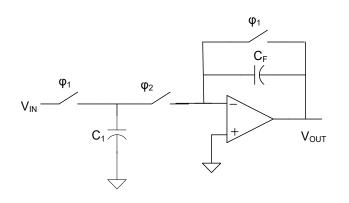

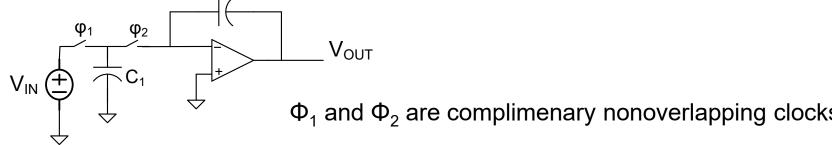

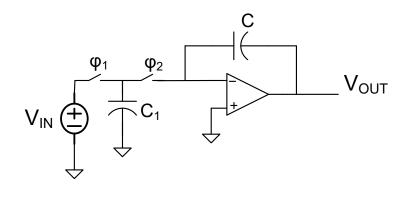

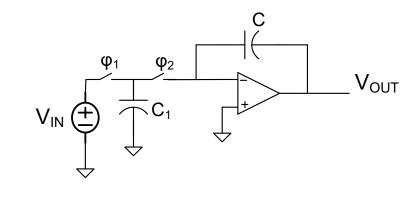

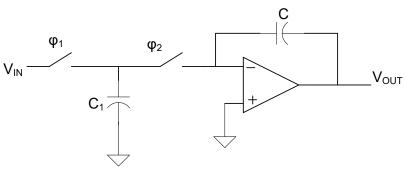

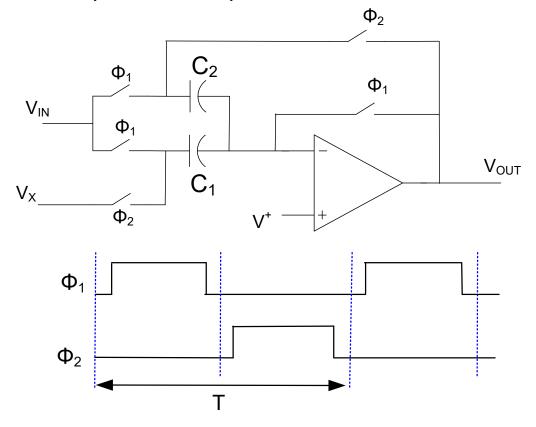

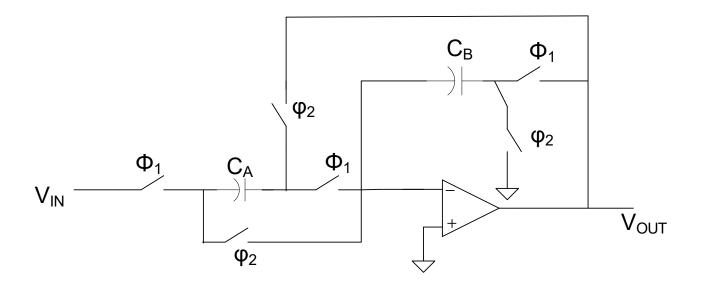

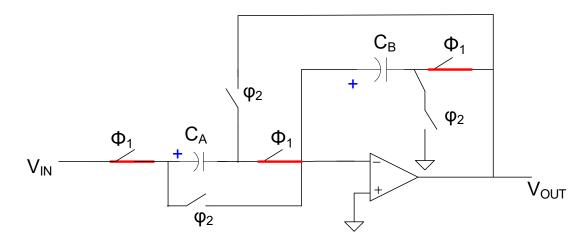

#### An amplifier alternative ?:

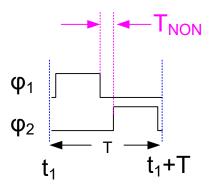

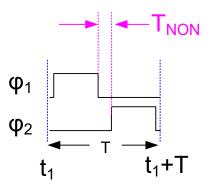

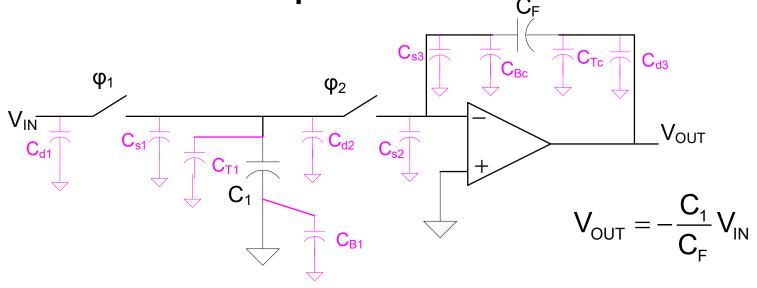

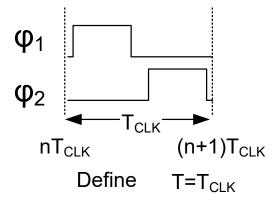

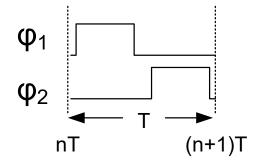

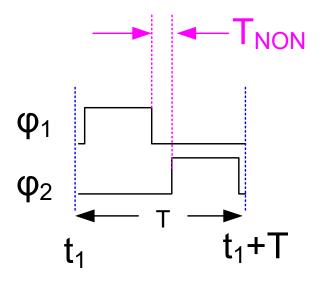

$\Phi_1$  and  $\Phi_2$  are nonoverlapping clocks

#### During Φ<sub>1</sub>

$C_1$  is charged to  $V_{IN}$  and stores charge  $Q_1 = C_1 V_{IN}$

$C_F$  is discharged and  $V_{OUT}=0$

#### During $\Phi_2$

C<sub>1</sub> is discharged but charge is transferred to C<sub>F</sub>

$$Q_2$$

=- $Q_1$  and  $V_{OUT}$ = $Q_2/C_F$

Substituting for  $Q_1$  we obtain  $V_{OUT} = -\frac{C_1}{C_F}V_{IN}$

Serves as a voltage amplifier with output valid during  $\phi_2$

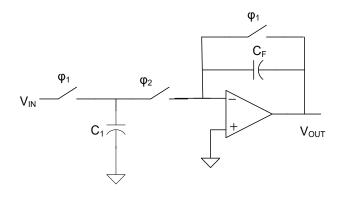

#### An amplifier alternative!

$$V_{OUT} = -\frac{C_1}{C_F} V_{IN}$$

$\Phi_1$  and  $\Phi_2$  are nonoverlapping clocks

- Many applications only need amplifier output at discrete points in time

- Accuracy can be very good

- Area can be very small

But, what about the switches?

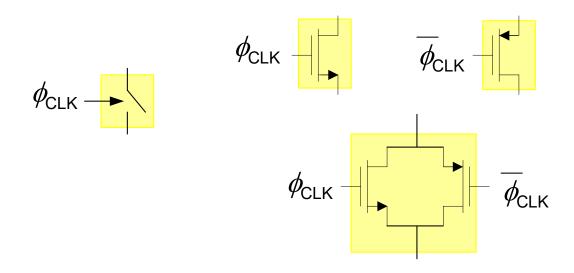

### Switches for SC Circuits

- Often a single MOS transistor is adequate (either n-ch or p-ch)

- Sometimes need transmission-gate switch (parallel n-ch and p-ch)

- Switches work very well and can be very small but must manage their R<sub>ON</sub>

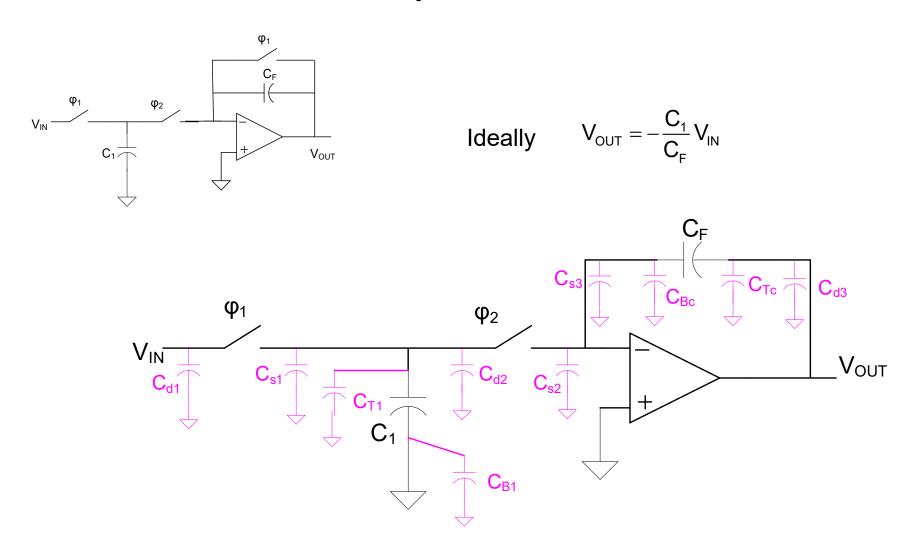

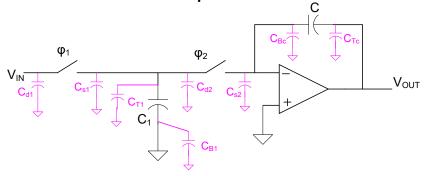

## Parasitic Capacitances

10 parasitic capacitances!

Some of parasitic capacitances may be several percent of the size of C<sub>1</sub> and C<sub>F</sub>

And parasitic capacitors do not match very well

## Parasitic Capacitances

10 parasitic capacitances!

Parasitic Capacitances

C<sub>1</sub>/C<sub>F</sub> can be very precisely controlled with appropriate layout and area allocation

If op amp is ideal,  $C_{d1}$ ,  $C_{B1}$ ,  $C_{s2}$ ,  $C_{s3}$ ,  $C_{Bc}$ ,  $C_{Tc}$  and  $C_{d3}$  do not affect charge transfer!

But C<sub>s1</sub>,C<sub>T1</sub>,C<sub>d2</sub> are all in parallel with C<sub>1</sub> and all transfer charge

$$V_{OUT} = -\frac{C_1 + (C_{s1} + C_{T1} + C_{d2})}{C_T}V_{IN}$$

Parasitic capacitances not accurately controlled and dramatically degrade matching!

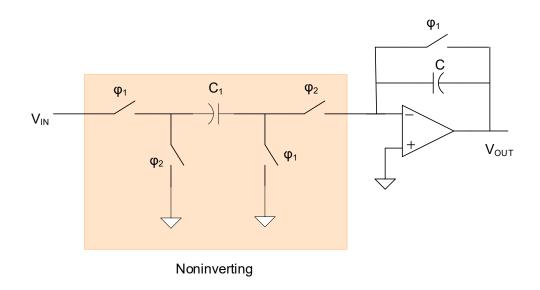

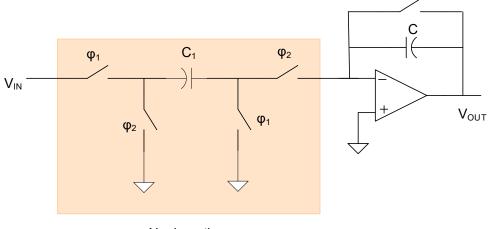

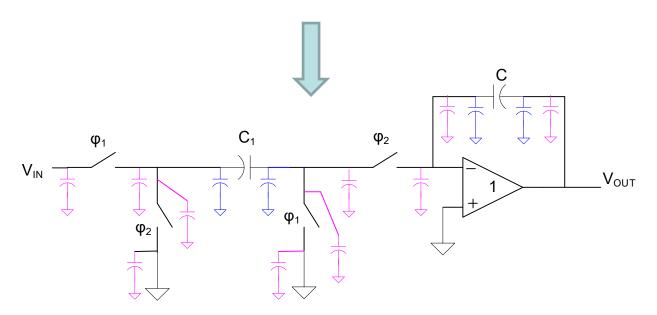

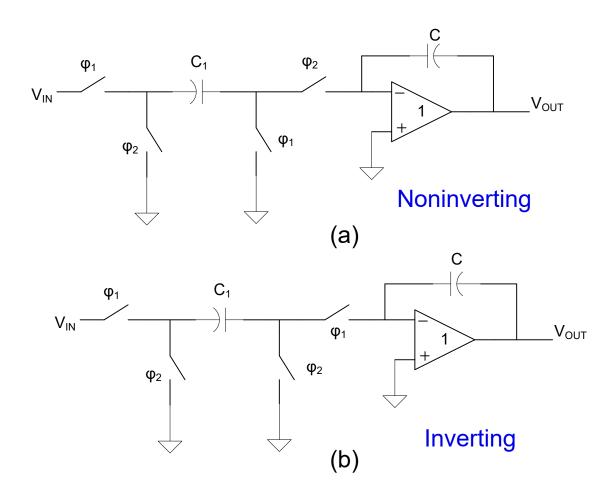

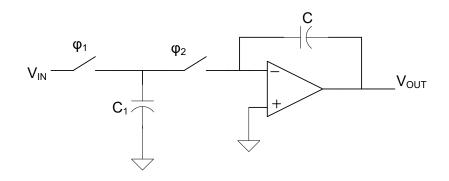

#### Stray Insensitive SC Amplifiers

Another SC Amplifier with even more switches!

Increased to 14 diffusion parasitic capacitances

#### Stray Insensitive SC Amplifiers

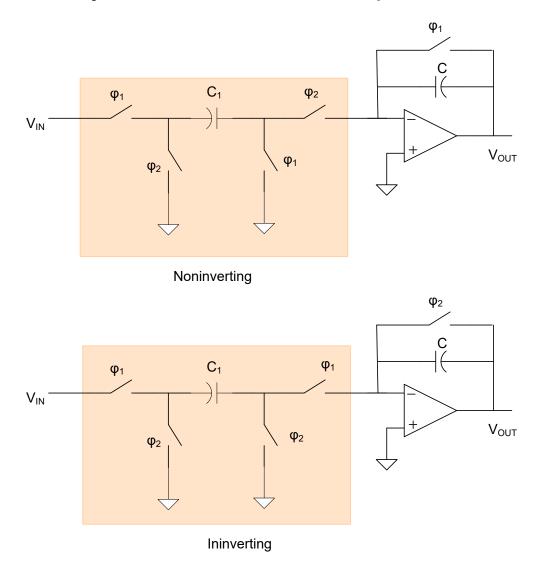

Noninverting

Can show that all 14 diffusion parasitic capacitances do not affect gain !!

#### Stray Insensitive SC Amplifiers

Can show that all diffusion parasitic capacitances do not affect gain

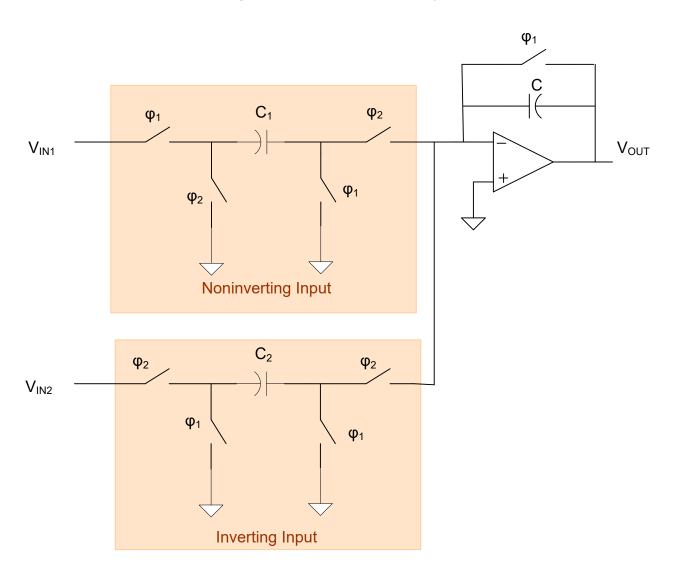

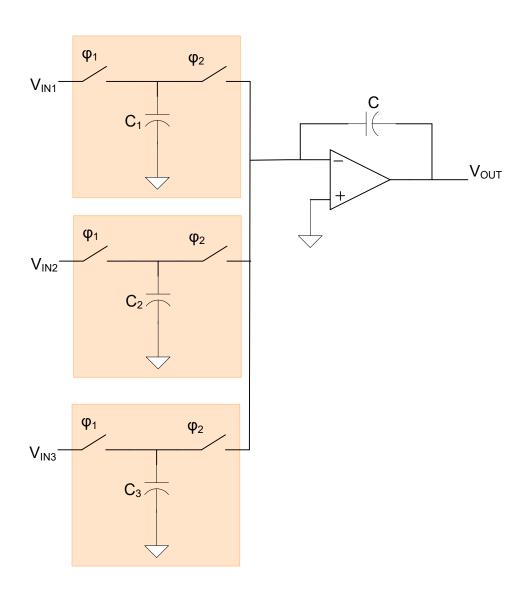

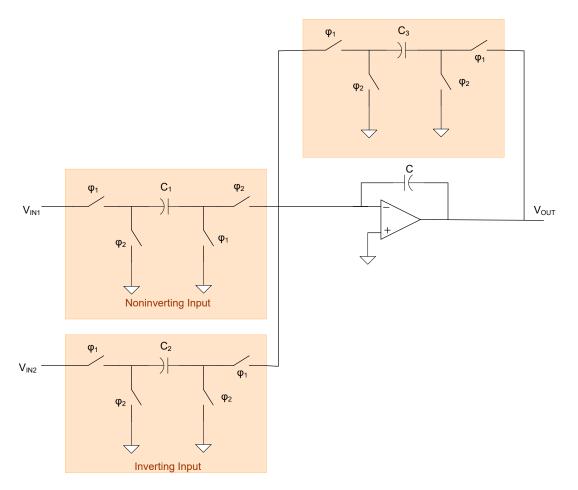

## Summing amplifier inputs either inverting or noninverting can be easily obtained

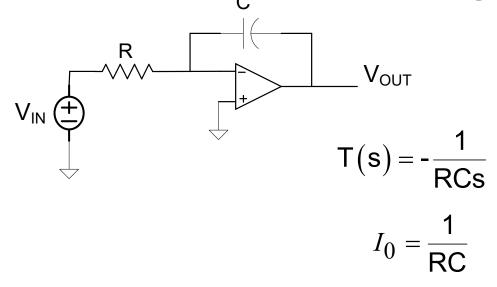

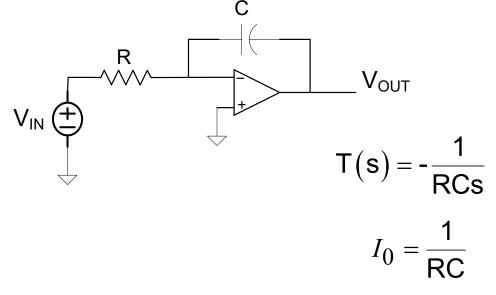

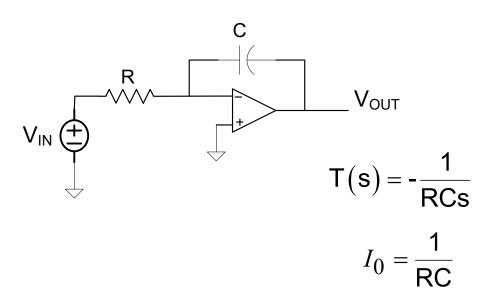

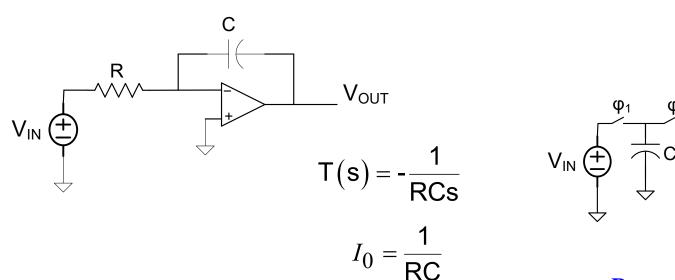

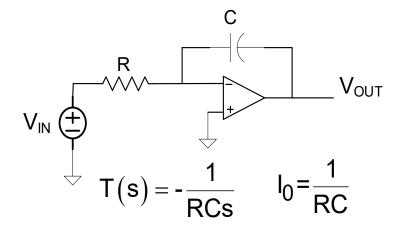

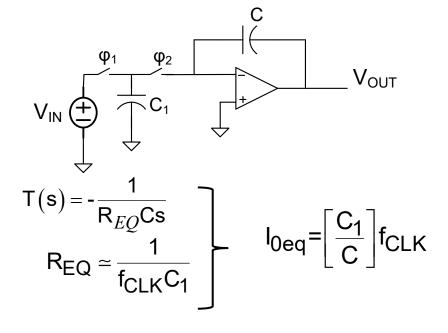

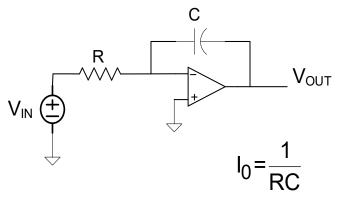

## Consider the Basic Integrator

Key performance of integrator (and integrator-based filters) is determined by the integrator time constant  $I_0$

Precision of time constants of a filter invariably determined by precision of I<sub>0</sub>

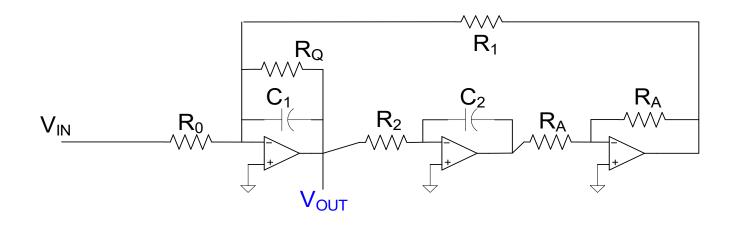

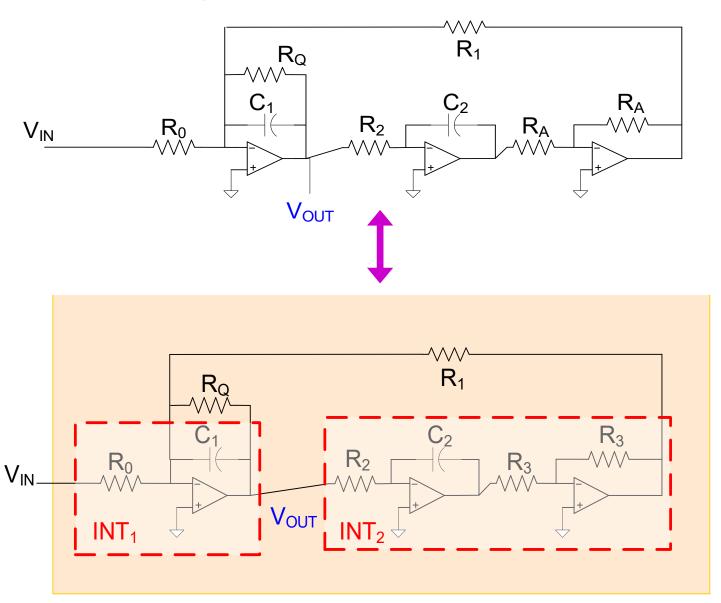

### Integrator-Based Filters:

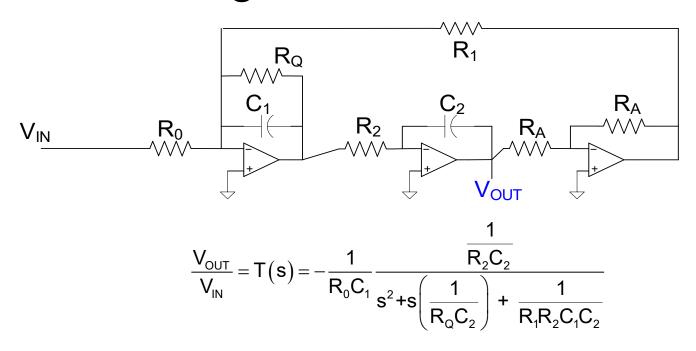

$$\frac{V_{\text{OUT}}}{V_{\text{IN}}} = T(s) = -\frac{1}{R_0 C_1} \frac{s}{s^2 + s \left(\frac{1}{R_Q C_2}\right) + \frac{1}{R_1 R_2 C_1 C_2}}$$

Second-order Bandpass Filter

Denote as a two-integrator-loop structure

## Integrator-Based Filters:

### Integrator-Based Filters:

Second-order Lowpass Filter

Denote as a two-integrator-loop structure

- Any filter transfer function can be implemented with integrators and summers

- Some of the best known filter structures are based upon integrators and summers

- Accuracy of RC products is critical in the design of good filters

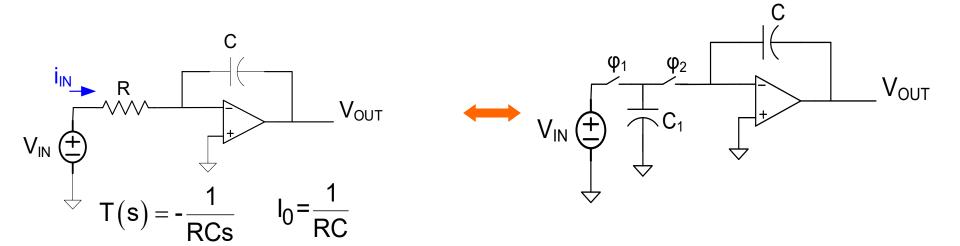

## Consider the Basic Integrator

Accurate control of I<sub>0</sub> is required to build good filters!

- 1. Accuracy of R and C difficult to accurately control particularly in integrated applications (often 2 or 3 orders of magnitude to variable)

- 2. Size of R and C unacceptably large if I<sub>0</sub> is in audio frequency range (2 or 3 orders of magnitude too large)

- 3. Amplifier GB limits performance

Incredible Challenge to Building Filters on Silicon!

## Integrator Design Issues

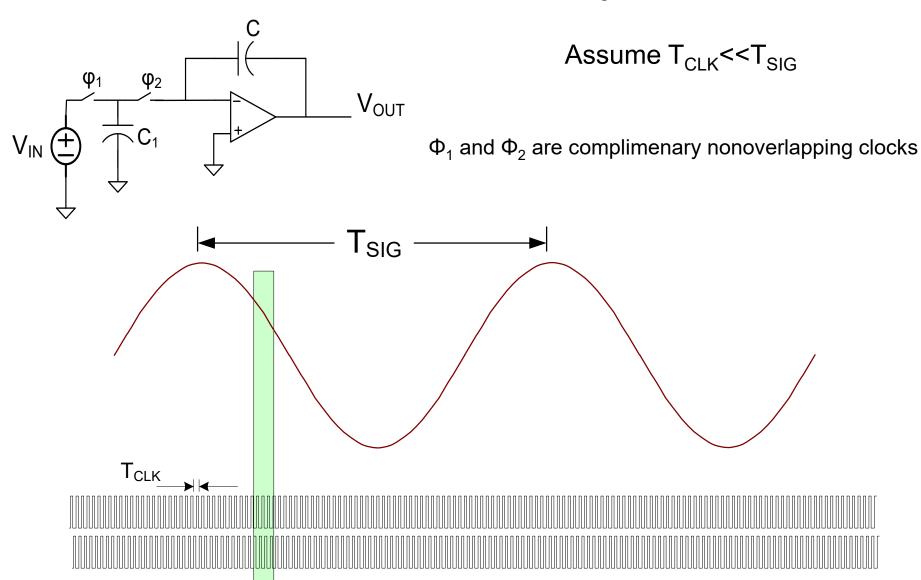

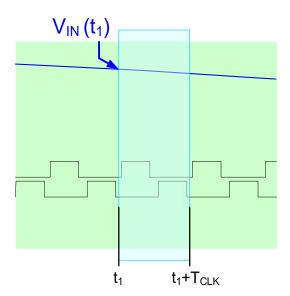

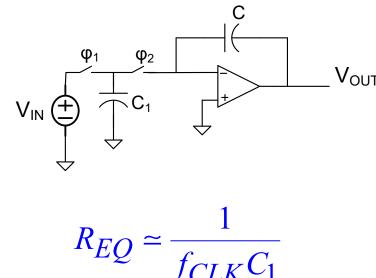

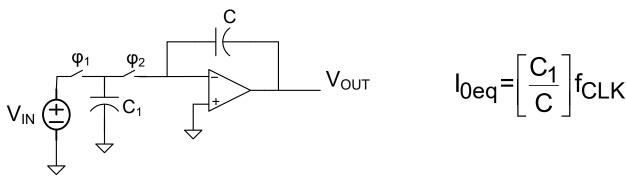

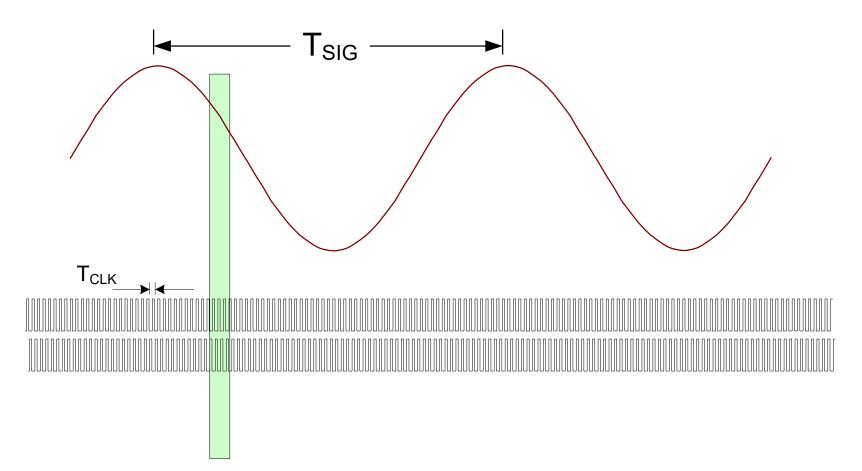

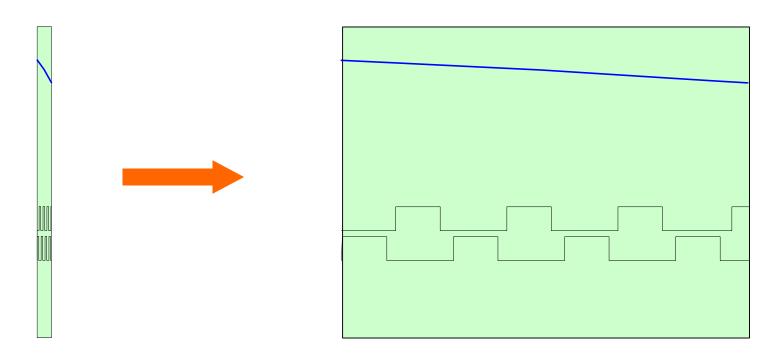

#### Consider:

Assume T<sub>CLK</sub><<T<sub>SIG</sub>

Termed a switched-capacitor circuit

## Consider the Switched-Capacitor Circuit

## Consider the Switched-Capacitor Circuit

# Compare the performance of the following two circuits

Consider the charge transferred to the feedback capacitor for both circuits in an interval of length T<sub>CLK</sub> at arbitrary time t<sub>1</sub>

For the RC circuit:

$$Q_{RC} = \int_{t_1}^{t_1 + T_{CLK}} i_{in}(t) dt$$

$$Q_{RC} = \int_{t_1}^{t_1 + T_{CLK}} \frac{V_{in}(t)}{R} dt$$

Since V<sub>in</sub> changes slowly assume input is constant over one clock period

$$Q_{RC} \simeq \int_{t_1}^{t_1+T_{CLK}} \frac{V_{in}(t_1)}{R} dt$$

$$Q_{RC} \simeq \left[\frac{V_{in}(t_1)}{R}\right]_{t_1}^{t_1+T_{CLK}} 1 dt$$

$$Q_{RC} \simeq \left[\frac{V_{in}(t_1)}{R}\right]_{t_1}^{T_{CLK}} 1 dt$$

Consider the charge transferred to the feedback capacitor for both circuits in an interval of length T<sub>CLK</sub> at time t<sub>1</sub>

For the RC circuit:

$$Q_{RC} \simeq \left\lceil \frac{V_{in}(t_1)}{R} \right\rceil T_{CLK}$$

Observe that a resistor "transfers" charge proportional to  $V_{\text{in}}$  in a short interval of  $T_{\text{CLK}}$

For the SC circuit

$$Q_{C1} = C_1 V_{in} \left( t_1 + \frac{T_{CLK}}{2} - \varepsilon \right)$$

Since V<sub>in</sub>(t) is slowly varying

$$Q_{C1} \simeq C_1 V_{in}\left(t_1\right)$$

But this is the charge that will be transferred to C during phase  $\Phi_2$

$$Q_{SC} \simeq C_1 V_{in}\left(t_1\right)$$

Observe that the SC circuit also transfers charge proportional to  $V_{\text{in}}$  in short intervals of length  $T_{\text{CLK}}$

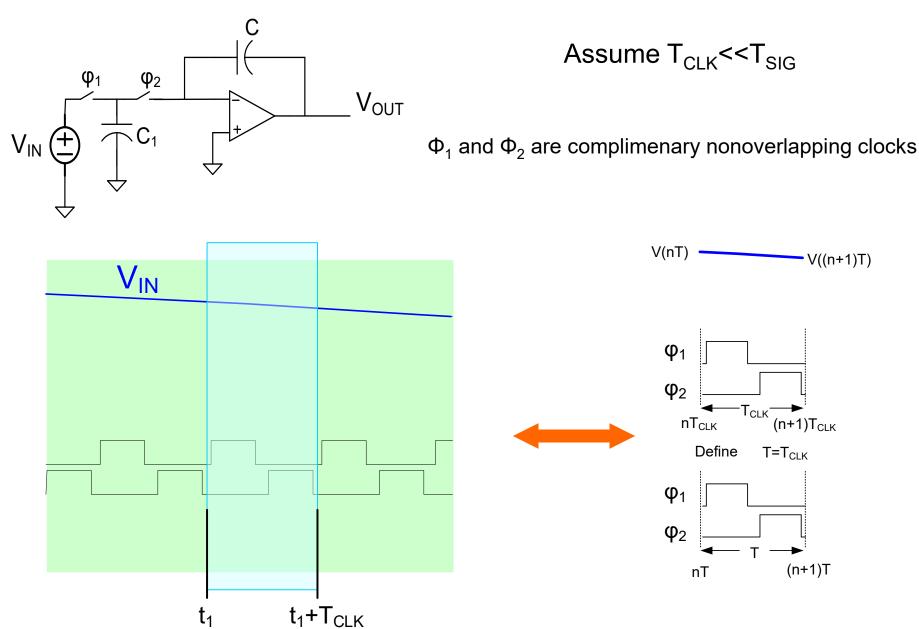

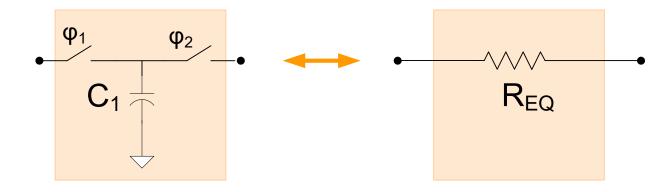

#### Comparing the two circuits

$$Q_{RC} \simeq \left\lceil \frac{V_{in}(t_1)}{R} \right\rceil T_{CLK} \qquad Q_{SC} \simeq C_1 V_{in}(t_1)$$

Equating charges since both proportional to V<sub>in</sub>(t<sub>1</sub>)

$$C_1 \simeq \left[\frac{1}{R}\right] T_{CLK}$$

$$R_{EQ} \simeq \frac{1}{f_{CLK} C_1}$$

Observe that a switched-capacitor behaves as a resistor!

This is an interesting observation that was made by Maxwell over 100 years ago but in and of itself was of almost no consequence

Note that large resistors require small capacitors!

This offers potential for overcoming <u>one</u> of the critical challenges for Implementing integrators on silicon at audio frequencies!

#### Equivalence Between Rapidly Switched Capacitor and Resistor

$$R_{EQ} \simeq \frac{1}{f_{CLK}C_1}$$

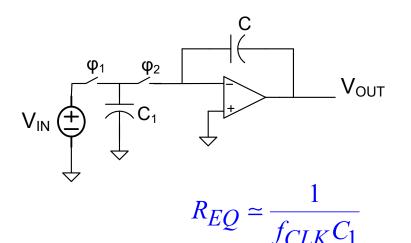

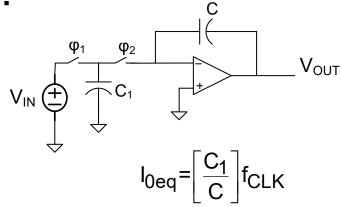

#### Consider again the SC integrator

$$\begin{split} T_{SC}(s) &\simeq \frac{-1}{R_{EQ}Cs} = -\frac{I_{0eq}}{s} \\ I_{0eq} &= \frac{1}{R_{EQ}C} \\ I_{0eq} &= \frac{1}{R_{EQ}C} = \frac{C_1 f_{CLK}}{C} \\ I_{0eq} &= \left[\frac{C_1}{C}\right] f_{CLK} \end{split}$$

This is a frequency referenced filter!

#### Consider again the SC integrator

- Accuracy of R and C difficult to accurately control (often 2 or 3 orders of magnitude to variable)

- 2. Area of R and C too large in audio frequency range (2 or 3 orders of magnitude too large)

- 3. Amplifier GB limits performance

- 1. Accuracy of cap ratio and f<sub>CLK</sub> very good

- 2. Area of C1 and C not too large

- 3. Amplifier GB limits performance less

### The Genius!!

- Accuracy of R and C difficult to accurately control (often 2 or 3 orders of magnitude to variable)

- 2. Area of R and C too large in audio frequency range (2 or 3 orders of magnitude too large)

- 3. Amplifier GB limits performance

- 1. Accuracy of cap ratio and f<sub>CLK</sub> very good

- 2. Area of C1 and C not too large

- 3. Amplifier GB limits performance less

Observation of Maxwell (and other "Me Too" up until 1977) on equivalence of resistor and switched capacitor had no impact

Two groups independently observed items 1) and 2) in 1976/1977 timeframe and realized that practical implementations on silicon were possible and that is the genius of the concept

Switched Capacitors and the corresponding charge redistribution circuits now used well beyond the SC filter field

Incredible enthusiasm and effort followed for better part of a decade

### sC integrator with summing inputs

### sC low-pass filter with summing inputs

#### Consider again the SC integrator

Observe this circuit has considerable parasitics

$$C_{1EQ} = C_1 + C_{s1} + C_{d2} + C_{T1}$$

Parasitic capacitors  $C_{s1}+C_{d2}+C_{T1}$  difficult to accurately match

- Parasitic capacitors of THIS SC integrator limit performance

- Other SC integrators (discussed later) ofter same benefits but are not affected by parasitic capacitors

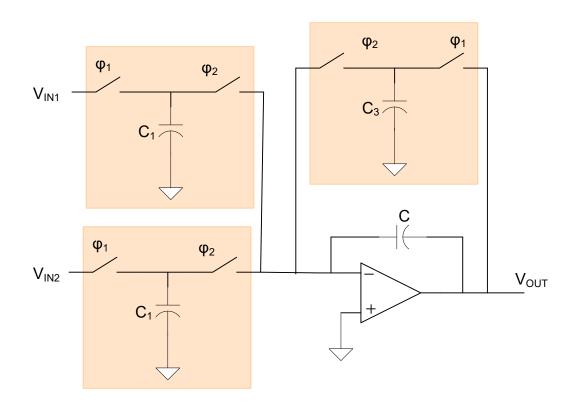

#### Stray insensitive Inverting and Noninverting SC integrators

# Stray Insensitive SC Low-Pass Filter with Inverting and Noninverting Inputs

Arbitrary number of inverting and ioninverting Inputs can be added

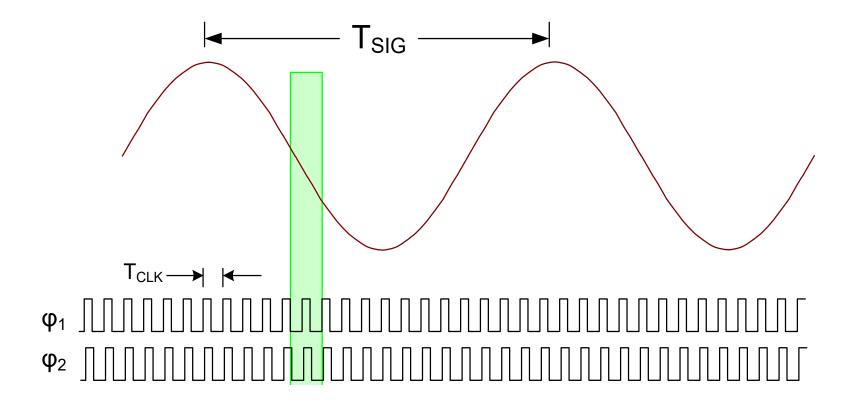

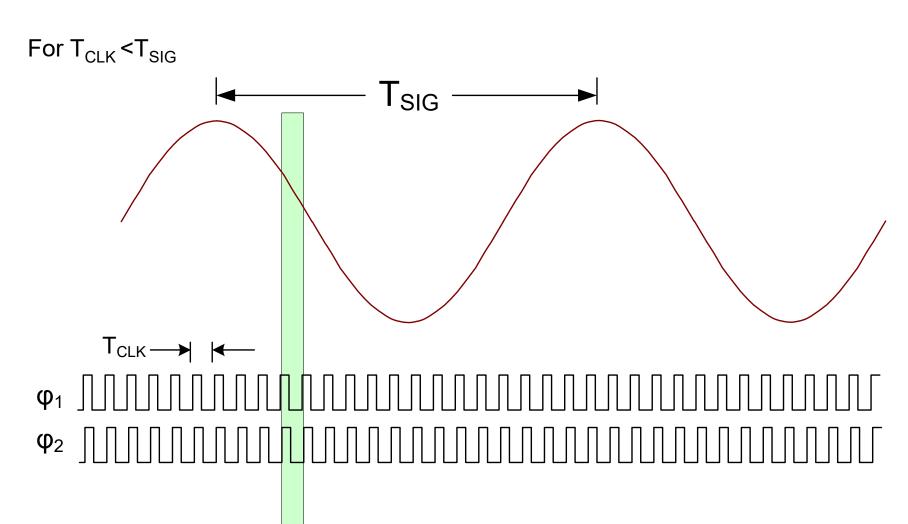

What if  $T_{CLK}$  is not much-much smaller than  $T_{SIG}$ ?

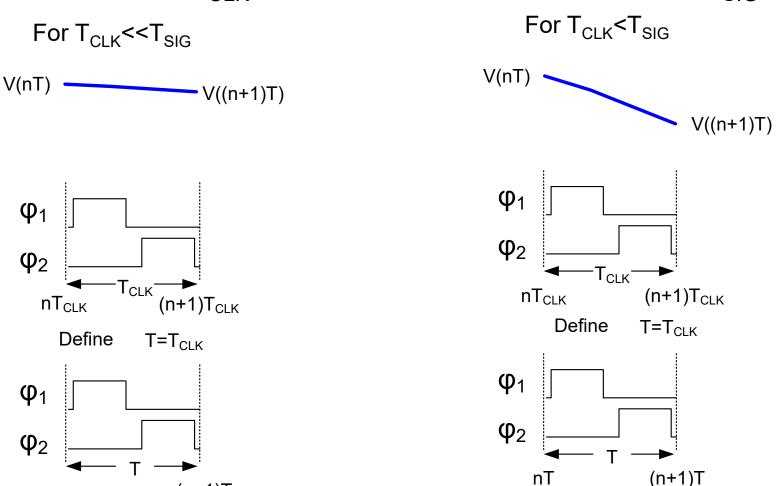

For T<sub>CLK</sub><<T<sub>SIG</sub>

What if T<sub>CLK</sub> is not much-much smaller than T<sub>SIG</sub>?

What if  $T_{CLK}$  is not much-much smaller than  $T_{SIG}$ ?

What if T<sub>CLK</sub> is not much-much smaller than T<sub>SIG</sub>?

What if  $T_{CLK}$  is not much-much smaller than  $T_{SIG}$ ?

(n+1)T

nT

Considerable change in V(t) in clock period

What if T<sub>CLK</sub> is not much-much smaller than T<sub>SIG</sub>?

$$V_0(nT+T) = V_0(nT) + \frac{\Delta Q}{C}$$

but  $-\Delta Q$  is the charge on  $C_1$  and the time  $\phi_1$  opens

$$-\Delta Q \simeq C_1 V_{IN} (nT+T/2)$$

$$V_{OUT}(nT+T)=V_{OUT}(nT)-(C_1/C)V_{IN}(nT+T/2)$$

If an input S/H,  $V_{IN}$  constant over periods of length T thus, assume  $V_{IN}(nT+T/2) \simeq V_{IN}(nT)$ So obtain

$$V_{OUT}(nT+T)=V_{OUT}(nT)-(C_1/C)V_{IN}(nT)$$

What if T<sub>CLK</sub> is not much-much smaller than T<sub>SIG</sub>?

$$V_{OUT}(nT+T)=V_{OUT}(nT)-(C_1/C)V_{IN}(nT)$$

for any T<sub>CLK</sub>, characterized in time domain by difference equation

or in frequency domain characterized by transfer function obtained by taking z-transform of the difference equation

$$H(z) = -\frac{\frac{C_1}{c}}{\frac{z-1}{c}}$$

What is really required for building a filter that has high-performance features?

#### Frequency domain:

Transfer function

$$T(s) = \frac{1}{RCs}$$

#### Time domain:

Differential Equation

$$V_{OUT}(t) = V_{OUT}(t_0) + \frac{1}{RC} \int_{t_0}^{t} V_{IN}(\tau) d\tau$$

Accurate control of polynomial coefficients in transfer function or accurate control of coefficients in the differential equation

What is really required for building a filter that has high-performance features?

#### Frequency domain:

**Transfer function**

$$T(s) = \frac{1}{RCs}$$

$$H(z) = -\frac{\frac{C_1}{2}}{\frac{z-1}{z-1}}$$

#### Time domain:

Differential Equation

$$V_{OUT}(t) = V_{OUT}(t_0) + \frac{1}{RC} \int_{t_0}^{t} V_{IN}(\tau) d\tau$$

Difference Equation

$$V_{OUT}(nT+T)=V_{OUT}(nT)-(C_1/C)V_{IN}(nT)$$

Accurate control of polynomial coefficients in transfer function or accurate control of coefficients in the differential/difference equation

What if T<sub>CLK</sub> is not much-much smaller than T<sub>SIG</sub>?

$$V_{OUT}(nT+T)=V_{OUT}(nT)-(C_1/C)V_{IN}(nT)$$

$$H(z) = -\frac{\frac{C_{1}}{c}}{\frac{z-1}{z-1}}$$

Switched-capacitor circuits have potential for good accuracy and attractive area irrespective of how  $T_{CLK}$  relates to  $T_{SIG}$

But good layout techniques and appropriate area need to be allocated to realize this potential!

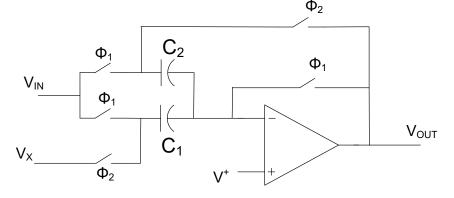

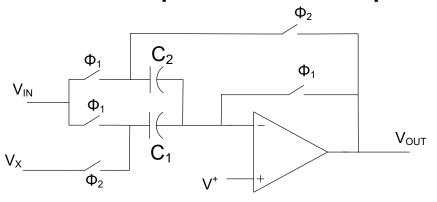

#### Consider the following circuit

Termed a flip-around amplifier

Clock signals are complimentary non-overlapping

# The flip-around amplifier $_{\Phi_{2}}$

### During Φ<sub>1</sub>

# The flip-around amplifier During $\Phi_1$

$$Q_1 = C_1 (V_{IN} - V^+)$$

$$Q_2 = C_2 (V_{IN} - V^+)$$

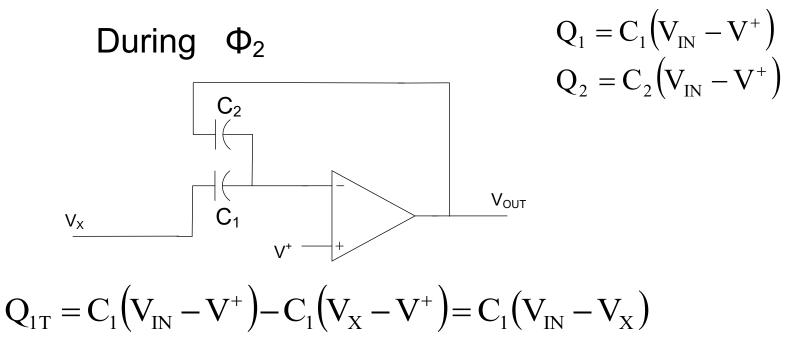

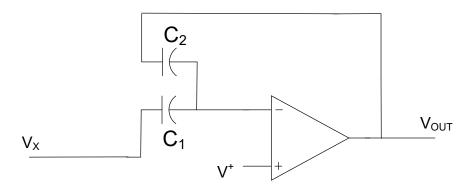

### The flip-around amplifier

#### During $\Phi_2$

#### The flip-around amplifier

$$Q_{2F} = Q_2 + Q_{1T} = C_2(V_{IN} - V^+) + C_1(V_{IN} - V_X) = (C_1 + C_2)V_{IN} - C_2V^+ - C_1V_X$$

#### The flip-around amplifier

#### During $\Phi_2$

$$Q_{2F} = Q_2 + Q_{1T} = C_2 (V_{IN} - V^+) + C_1 (V_{IN} - V_X) = (C_1 + C_2) V_{IN} - C_2 V^+ - C_1 V_X$$

$$V_{C2F} = \frac{Q_{2F}}{C_2} = \left(1 + \frac{C_1}{C_2}\right) V_{IN} - V^+ - \frac{C_1}{C_2} V_X$$

$$V_{\text{OUTF}} = V_{\text{C2F}} + V^{+} = \left(1 + \frac{C_{1}}{C_{2}}\right) V_{\text{IN}} - \frac{C_{1}}{C_{2}} V_{\text{X}}$$

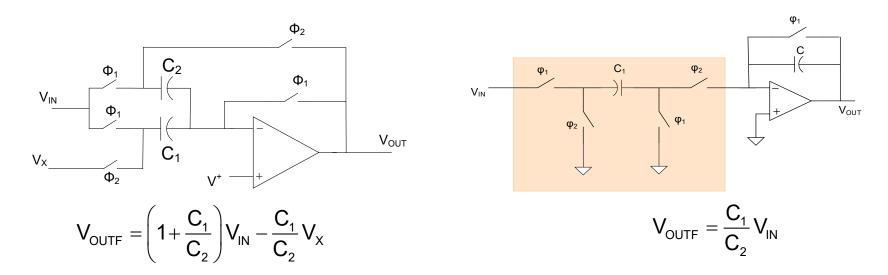

#### Comparison of Flip Around Amplifier with previous SC amplifier

If  $V_X$ =0, both have a positive gain but somewhat more gain for a given capacitor ratio for the flip-around structure

In both cases, gain accuracy dependent upon how closely the capacitor ratios can be controlled

One particularly useful application is where want dc gain equal to 2 (1-bit/stage pipeline ADC)

Flip-around requires matching two capacitors, other requires ratio matching of two capacitors

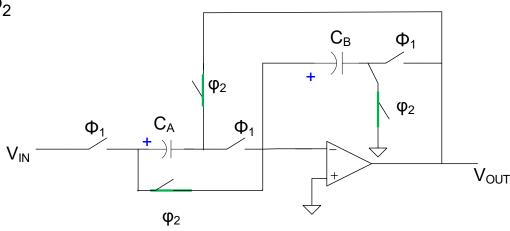

#### Another Flip Around Amplifier

Clock signals are complimentary non-overlapping

#### **Another Flip Around Amplifier**

During phase φ<sub>1</sub>

Assume C<sub>B</sub> discharged at start of phase – must verify later

$$\begin{aligned} \boldsymbol{Q}_{\text{CA1}} &= \boldsymbol{C}_{\text{A}} \boldsymbol{V}_{\text{IN}} \\ \boldsymbol{Q}_{\text{CB1}} &= \boldsymbol{C}_{\text{A}} \boldsymbol{V}_{\text{IN}} \end{aligned}$$

$$V_{\text{OUT}} = -\frac{Q_{\text{CB1}}}{C_{\text{B}}} = -\frac{C_{\text{A}}}{C_{\text{B}}}V_{\text{IN}}$$

#### **Another Flip Around Amplifier**

During phase φ<sub>2</sub>

From phase  $\phi_1$   $Q_{CA1} = C_A V_{IN}$   $Q_{CB1} = C_A V_{IN}$

$$Q_{CA2} = Q_{CA1} + Q_{CB1}$$

$$Q_{CB2} = 0$$

$$V_{\text{OUT}} = -\frac{Q_{\text{CA2}}}{C_{\text{A}}}$$

$$V_{\text{CB}} = 0$$

Verified that  $C_B$  was discharged at the start of phase  $\phi_1$

$$V_{\text{OUT}} = -\frac{C_{\text{A}}V_{\text{IN}} + C_{\text{A}}V_{\text{IN}}}{C_{\text{A}}} = -2V_{\text{IN}}$$

This structure has a gain of 2 independent of any capacitor matching!

Can modify to get noninverting gain and gains of 3, 4, .., without matching requirements

### Non-overlapping Clocks

- Essential that the clocks be non-overlapping

- Simple inverter to derive the complimentary clock will not work

- Must guarantee non-overlap in the presence of PVT variations

- In non-demanding speed applications,  $\varphi_1$  and  $\varphi_2$  will have 25% duty cycles

Stay Safe and Stay Healthy!

### End of Lecture 40